a FREE **e-newsletter**

your FREE magazine

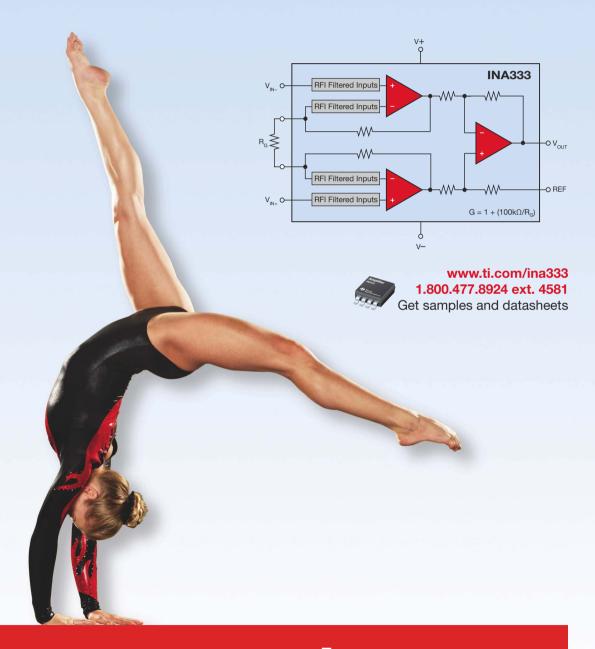

## Integrate Your Inputs

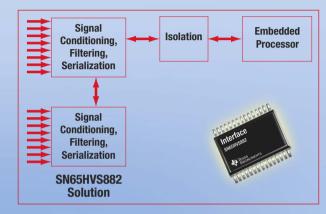

### First 8-channel digital-input serializer

The **SN65HVS882** from Texas Instruments is the industry's first eight-channel, digital-input serializer. Integrated features reduce the number of required components, save up to 60 percent of board space, and create a flexible, cost-effective solution. Simplify your design process and speed time to market with the highest input density device in the industry, the SN65HVS882 from TI. **High-Performance Analog>>Your Way™.**

www.ti.com/sn65hvs882 1.800.477.8924 ext. 4578 Get samples and evaluation modules

Hundreds-of-thousands of parts in stock. Visit www.digikey.com today to see how many!

Quality Electronic Components, Superior Service

Digi-Key Corporation purchases <u>all product</u> directly from its <u>original manufacturer</u>.

www.digikey.com

1.800.344.4539

## **Design Simply**

## **Design Completely**

## Design Today

### The Virtex®-5 Family: The Ultimate System Integration Platform

- Increase Your System Performance

- Lower Your System Cost

- Design with Ease

The Virtex-5 family delivers unparalleled system integration capabilities for driving your most mission-critical, high-performance applications. With a choice of four platforms optimized for logic, serial connectivity, DSP and embedded processing with hardened PowerPC® 440 processor blocks, the Virtex-5 family delivers an unprecedented combination of flexibility and performance—backed by world class application support.

Only the Virtex-5 family offers you a complete suite of design solutions built on proven 65nm technology in devices shipping today.

Get started on your Virtex-5 design. Visit www.xilinx.com/ise for a free 60 day evaluation of any ISE® Design Suite 10.1 product.

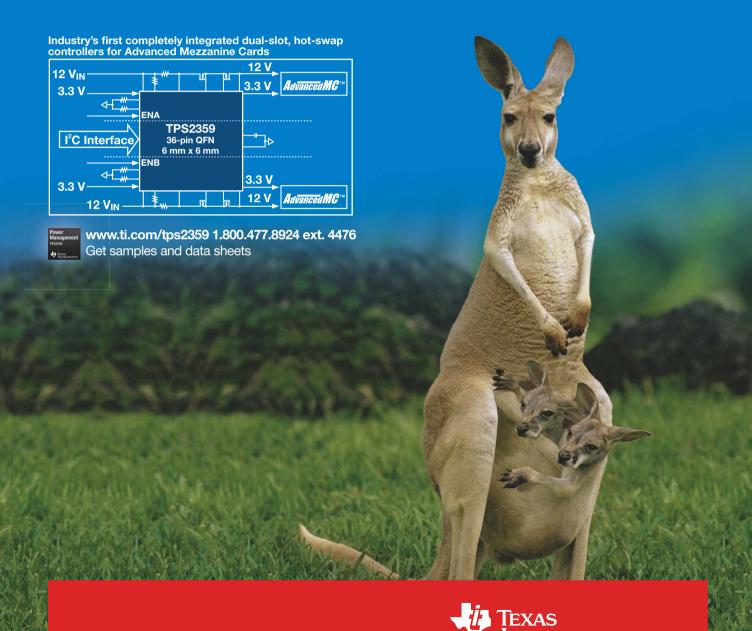

## **Dual-Slot Hot Swap**

### The Naturally Integrated Solution for AdvancedMC™

The **TPS2358/9** dual-slot controllers from Texas Instruments manage two 12-V rails and two 3.3-V rails for Advanced Mezzanine Cards in ATCA,  $\mu$ TCA or custom systems. These devices are easy-to-use ATCA/ $\mu$ TCA-compliant solutions with hot swap, ORing and status indicators for all four paths. Optional I²C interface provides programmability and monitoring with the highest integration, flexibility and performance in one small package. **That's High-Performance Analog>>Your Way<sup>TM</sup>**.

### And our 34401A is now even better looking

Agilent's 34401A DMM, the long-held industry standard, now sports a new look along with a 9% price cut. And the high performance 34410A is 19% less than it was before. Take advantage of these new prices today; go to www.agilent.com/ find/dmmcompare

|                                   | 10000000  | Concesso Con   |

|-----------------------------------|-----------|----------------|

| Specification                     | 34405A    | 34401A         |

| Resolution                        | 5½ digits | 6½ digits      |

| Basic DC<br>Accuracy              | 250 ppm   | 35 ppm         |

| Max Readings/s (continuous to PC) | 19        | 1,000          |

| Connectivity                      | USB       | GPIB<br>RS-232 |

| Price                             | \$745*    | \$1,070*       |

| 100000 + K     | [1000000 F3C                  | 1000000 FRE                   |

|----------------|-------------------------------|-------------------------------|

| 34401A         | 34410A                        | 34411A                        |

| 6½ digits      | 6½ digits<br>dual display     | 6½ digits<br>dual display     |

| 35 ppm         | 30 ppm                        | 30 ppm                        |

| 1,000          | 10,000                        | 50,000                        |

| GPIB<br>RS-232 | GPIB, USB, LAN<br>LXI Class C | GPIB, USB, LAN<br>LXI Class C |

| 1,070*         | \$1,295*                      | \$1,995*                      |

<sup>\*</sup> Prices in USD and subject to change

Agilent Authorized Distributor

## EDN contents

8,21,08

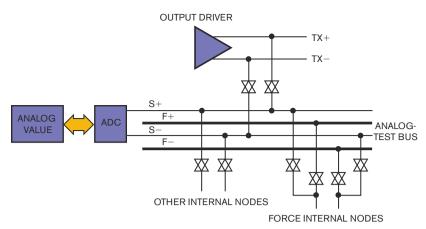

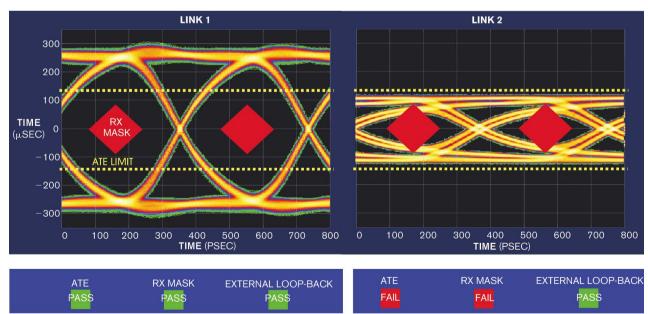

On-chip test capabilities solve the analog-test problem for highspeed serial interfaces

Including analog-test hardware in an SOC provides visibility into the performance of on-chip serial links, helping to ensure signal integrity and reduce the cost of manufacturing test.

by Navraj Nandra, Synopsys Inc.

#### Electronic-systemlevel design: Is there fire beneath the smoke?

After years of overclaiming and underperforming, ESL design has a role in many design flows. But has anyone noticed? by Ron Wilson, Executive Editor

#### Lithium-ion technology targets portable power

Work closely with your lithium-ion-cell manufacturer and batterypack-design house to develop safety and performance features for your system's battery pack. by Margery Conner, Technical Editor

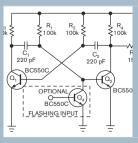

## ESIGNIDEAS

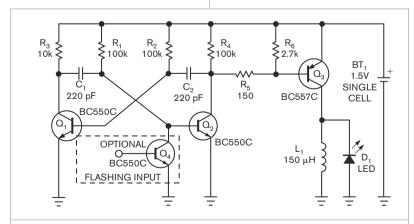

- 53 Astable multivibrator lights LED from a single cell

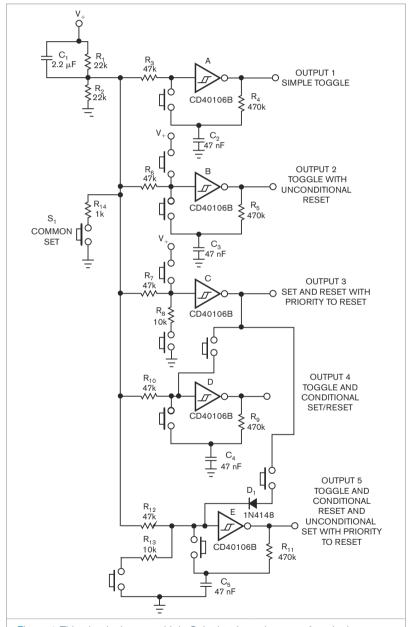

- 54 IC provides versatile toggle functions

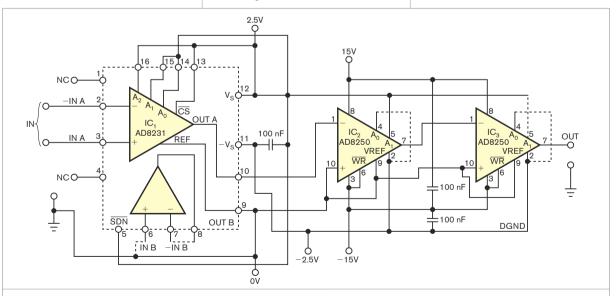

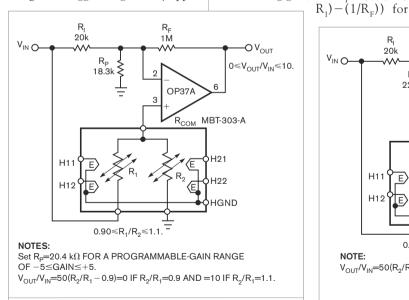

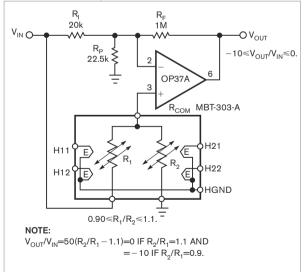

- 56 Instrumentation amp has low offset, drift, and low-frequency noise

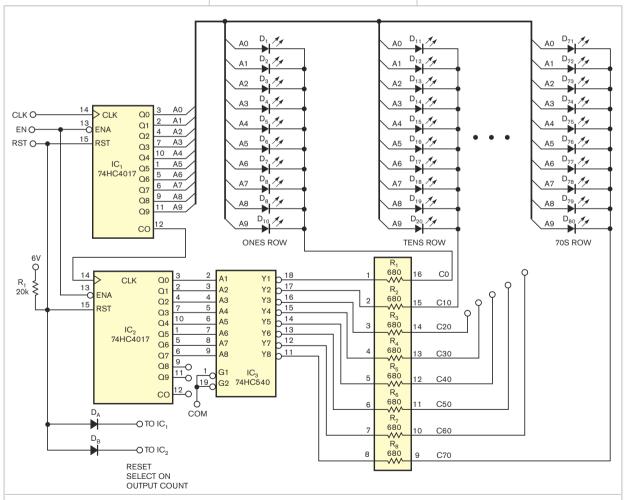

- 58 Four DIPs provide as many as 80 sequential-LED outputs

- 59 Program an op-amp gain block with a limited-adjustability, monolithic, solid-state resistor

### "Sweating the details" redefined by Toshiba.

Toshiba sweats every detail in order to deliver expert, responsive technical service/support for its electronic components. The Toshiba design centers have a team of engineers dedicated to power analysis to ensure optimum power management. Toshiba Virtual Prototyping—our exclusive system for chip/package/system co-design for Custom SoCs—delivers a poweroptimized model usually in less than eight weeks. And we employ advanced

low-power design techniques like Multi-Vth, Clock Gating and much more. This commitment to delivering unmatched technical expertise is our formula for customer success.

> Which equation below is the most accurate estimate for power consumed by flip flops on a chip? Use the legend at transform.toshiba.com to solve the equation and win a hoody sweat shirt (while supplies last).

a)  $P_{ff} = m(C_{ff}V_{c}^{2}F + C_{I}V_{c}^{2}F + I_{ff}V_{c})$ b)  $P_{ff} = m(C_{ff}V_{c}^{2}F + C_{l}V_{c}^{2}F/_{2} + I_{ff}V_{c})$ c)  $P = M(C_{st}V_{c}^{2}F + C_{l}V_{c}^{2} + I_{st}V_{c}) + nC_{ct}V_{c}^{2}F$ d)  $P_{ss}^{-m}(C_{ss}V_{c}^{2}F+PC_{l}V_{c}^{2}F/2+I_{ss}V_{c})+nC_{cs}V_{c}^{2}F$

Staff Design Engineer, Toshiba America Electronic Components, Inc.

TOSHIBA Leading Innovation >>>

### contents 8.21.08

- Lithium-ion capacitor combines more than 100,000 charge cycles, low self-discharge rate

- 15 FPGA IP completes wireless-backhaul method

- 16 Keithley debuts software upgrade and switch/multimeter options

- 18 16-bit, 10M-sample/sec ADC uses SAR architecture

- 18 Multiarchitecture-DSP road map refines power-efficiency-versus-performance balance

- 20 Research Update: Photonics researchers decelerate light to accelerate data; Technology gives windows a solar edge; Kerf-free wafering technology reduces polysilicon for photovoltaics

## DEPARTMENTS & COLUMNS

- 10 **EDN.comment:** Hang up and drive; hang up and walk

- 22 **Signal Integrity:** All about surface-mount ferrites

- 24 **Tapeout:** IP selection and power supplies

- 60 **Supply Chain:** Organic-distributor growth remains steady in unsteady times; Consumer telematics shifts to in-car connectivity; IPC Brussels meeting reveals ROHS-revisions concerns

- 66 Tales from the Cube: It's an electromagneticmechanical world

## PRODUCT ROUNDUP

- 62 Switches and Relays: Pendulum-style detection switches, Hall-effect-IC switches, load switches, terminal-block relays, USB/104 I/O solid-state relay-output modules, and more

- 63 Embedded Systems: MicroTCA carrier hubs, dataacquisition boards, and rack-mount computers

EDN® (ISSN#0012-7516), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Fark Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 B Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2008 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year (includes 7% GST, GST#123397457), Mexico, \$215 one year, air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc., used under license. A Reed Business Information Publication/Volume 53, Number 17 (Printed in USA).

How's less than 0.3Ω! Panasonic PhotoMOS™ relays have *the* lowest on-resistance available, perfect for high performance switching applications. Fast switching speed, low capacitance, a broad range of devices and all from a company known for innovation. How low can we go? Stay connected at http://pewa.panasonic.com/pm02 to find out!

**FREE** samples available!

#### **Panasonic Electric Works**

Call: 800-276-6289 http://pewa.panasonic.com/pm02 info@us.pewg.panasonic.com **Panasonic ideas for life**

## at edn.com

EXPANDED ENGINEERING COVERAGE PLUS DAILY NEWS, BLOGS, VIDEO, AND MORE.

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Intel details PC-graphics-aimed Larrabee

Intel's forthcoming multicore Larrabee architecture includes a new approach to the software-rendering 3-D pipeline, a many-core programming model, and performance analysis for several applications. → www.edn.com/article/CA6584166

#### Selecting op amps for high-speed ATE digitizers

→www.edn.com/article/CA6583378

#### Structured-ASIC option reaches 45-nm node

→www.edn.com/article/CA6584047

#### Low-power DDR2-DRAM momentum begins to build

→www.edn.com/article/CA6581906

#### Cypress' TJ Rodgers: Programmability, politics, and profitability

→www.edn.com/article/CA6584366

#### Engineering tops list of college degrees ranked by salary

→www.edn.com/080821toc1

**NEED DESIGN IDEAS?**

## Read the latest Design Ideas, search our archive that spans more than 14 years, and learn how to submit your own. →www.edn.com/designideas

A selection of recent articles receiving high traffic on www.edn.com.

#### Magnetic measurement tools attract attention

Measuring magnetic fields requires specialized sensors and knowledge of physics and electronics. You can use a variety of instruments, including gaussmeters, teslameters, fluxmeters, and magnetometers, to measure magnetism, and prices for these units range from pennies to hundreds of thousands of dollars.

→www.edn.com/article/CA6578134

#### Red LEDs function as light sensors

→www.edn.com/article/CA6541376

#### Intel marches once again into microcontroller market

→www.edn.com/article/CA6581313

#### CherryPal challenges PC tradition with 2W "ultragreen" offering

→www.edn.com/article/CA6580041

#### Plug-in hybrid vehicles: Here's what GM's thinking

→www.edn.com/080821toc2

#### File your own patents

→www.edn.com/blog/080821toc3

#### Achieve femtoampere leakage in surface-mount-op-amp layouts

→ www.edn.com/article/CA6579596

#### **ELECTRONIC NEWS TODAY**

The latest tech news, delivered every afternoon.

→www.edn.com/newsletters

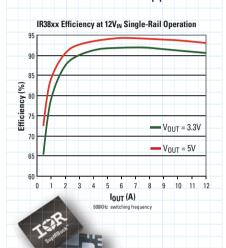

## **High Density** and High **Performance**

IR's Sup*IR*Buck™ Integrated Regulators deliver benchmark efficiency for data center and consumer applications

#### SupIRBuck Advantages:

- Integrates IR's high performance synchronous buck control ICs and benchmark HEXFET® trench technology MOSFETs

- 8-10% higher efficiency compared to monolithic Power IC two-stage solution

- · High density compared to equivalent discrete solution

For more information call 1 800 981 8699 or visit us at www.irf.com/dcdc

#### BY RICK NELSON, EDITOR-IN-CHIEF

## Hang up and drive; hang up and walk

he cell-phone market is potentially huge. Sanjay K Jha, then chief operating officer of Qualcomm and president of Qualcomm CDMA Technology, said in a June 11 Design Automation Conference keynote address that 2 billion people are wireless subscribers today and that, by 2020, 9 billion people will become potential customers. (Motorola has subsequently hired Jha to serve as co-chief executive officer.) Jha cited one downside to this exploding market: Many of these 9 billion potential subscribers won't spend more than \$15 or \$20 for their handsets.

There is another: Many of these 9 billion will be talking while driving or texting while walking, creating mayhem on the roads and sidewalks.

The growing cell-phone-related mayhem has already drawn attention of legislatures in the United States, and, on July 1, laws banning the use of handheld phones while driving went into effect in California and Washington, complementing laws already in effect in Connecticut, the District of Columbia, New Jersey, New York, and Utah.

Don't get me wrong. I think people talking while driving can be a menace. Unfortunately, however, the laws taking effect don't address the real problem.

The online magazine *Salon* (www. salon.com) recently covered this phenomenon (**Reference 1**). "For years, psychologists who study driving and attention have argued that switching to 'hands free' is not a real solution to the hazards caused by yakking on the mobile in the car," the author, Katharine Mieszkowski, states. She quotes David Strayer, professor of psychology at the University of Utah: "The im-

A company has been outfitting lampposts in London's East End with padded bumpers to reduce injuries to ambulatory texters.

pairments aren't because your hands aren't on the wheel. It's because your mind isn't on the road"—a contention backed up by magnetic-resonance-imaging experiments that show that conversations distract parts of the brain involved in driving.

Mieszkowski also notes that talking on a cell phone while driving is more dangerous than talking with incar passengers. Passengers, she writes, modulate their conversation in accordance to road conditions, having their own safety in mind. In addition, she quotes Paul Atchley, professor of psychology at the University of Kansas: "Cell-phone conversations are more intense than in-car conversation."

Cell-phone conversations have more words per minute, and a driver who stops conversing to deal with traffic will be accosted at exactly the wrong time with "Hey, are you still there?"

I would assume that laws mandating hands-free cell-phone operation would inherently outlaw texting while driving, and that's a good thing. It turns out, however, that many texting-related accidents don't involve texting while driving. In another recent article (Reference 2), author Dionne Searcey writes: "A growing group of multitaskers are texting on the go ... while ambulatory. They obliviously ram into walls and doorways or fall down stairs. Out on the streets, they bump into lampposts, parked cars, garbage cans, and other stationary objects."

So what's the solution? Searcey reports that a company has been outfitting lampposts in London's East End with padded bumpers to reduce injuries to ambulatory texters. Well, that's one approach, and it's likely to be more effective than US handsfree-cell-phone laws targeting drivers. For both mobile texters and mobile talkers, however, education, not legislation, would seem to be the more promising road to take.EDN

#### REFERENCES

- Mieszkowski, Katharine, "Hang up and drive," *Salon*, July 25, 2008, www.salon.com/news/feature/ 2008/07/25/cell\_phone\_driving/index.html.

- Searcey, Dionne, "Generation Text: Emailing on the Go Sends Some Users Into Harm's Way," The Wall Street Journal, July 25, 2008, www.wsj.com.

Contact me at rnelson@reedbusiness.com.

- + Go to www.edn.com/080821ed and click on Feedback Loop to post a comment on this column.

- + More at www.edn.com/edncomment

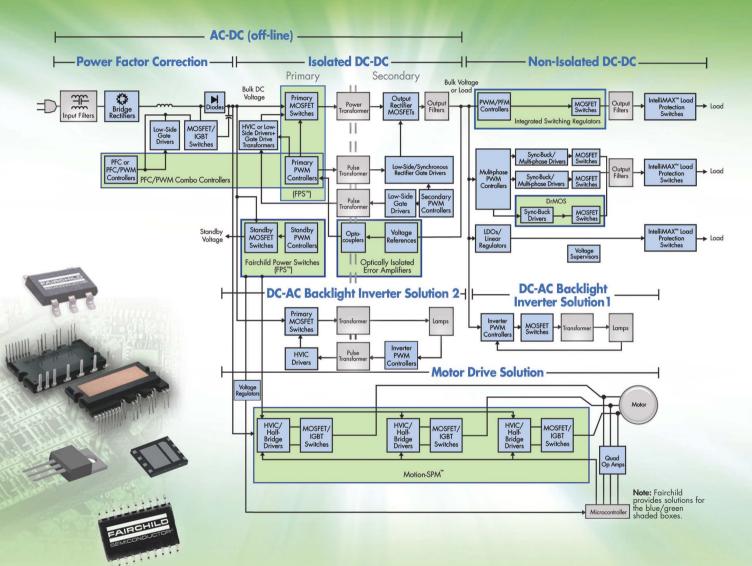

## 1000s of products, 1 goal: energy efficiency

Energy-efficient solutions for designers. And their 6 billion neighbors.

From power analog and power discrete products to online tools and FAEs, Fairchild has the resources you need to develop energy-efficient designs for power-sensitive applications.

To download Fairchild's Power Solutions Brochure, please visit www.fairchildsemi.com/power.

## LATE DELIVERY A PROBLEM?

\*UPS Ground only.

## Find all your product solutions @ Allied

alliedelec<sub>k</sub>com

1.800.433.5700 We do more than take your order

#### PRESIDENT ROSTON DIVISION PEED BUSINESS INFORMATION

Mark Finkelstein, mark.finkelstein@reedbusiness.com

1-781-734-8431

#### PUBLISHER. EDN WORLDWIDE

Russell F Pratt. 1-781-734-8417 rpratt@reedbusiness.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-408-345-4437; iudy haves@reedhusiness.com

#### VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field. 1-781-734-8188: kfield@reedbusiness.com

#### EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

#### EXECUTIVE EDITOR

Ron Wilson, 1-408-345-4427: ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

#### EDITOR-IN-CHIEF, EDN.COM

Matthew Miller 1-781-734-8446: fax: 1-303-265-3017: mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713: fax: 1-858-486-3646: wwebb@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor

1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcrayotta@edn.com

#### NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### SEMICONDUCTOR MANUFACTURING AND DESIGN

Ann Steffora Mutschler, Senior Editor 1-408-345-4436; ann.mutschler@reedbusiness.com

#### DESIGN IDEAS EDITOR

Martin Rowe edndesignidegs@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439: fax: 1-303-265-3131: f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523;

#### mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-303-265-3198 Melissa Annand Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279

Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson PhD: Bonnie Baker-Joshua Israelsohn; Pallab Chatterjee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager

1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager 1-781-734-8332: fax: 1-303-265-3015

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

Susie Newham, Managing Director susie newham@rhi-asia.com Kirtimava Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### DENNIS BROPHY

Director of Business Development, Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV

#### System Architect, Intel

PON MANCINI

#### Retired Staff Scientist

GABRIEL PATULEA

#### Design Engineer, Cisco

DAVE ROBERTSON Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

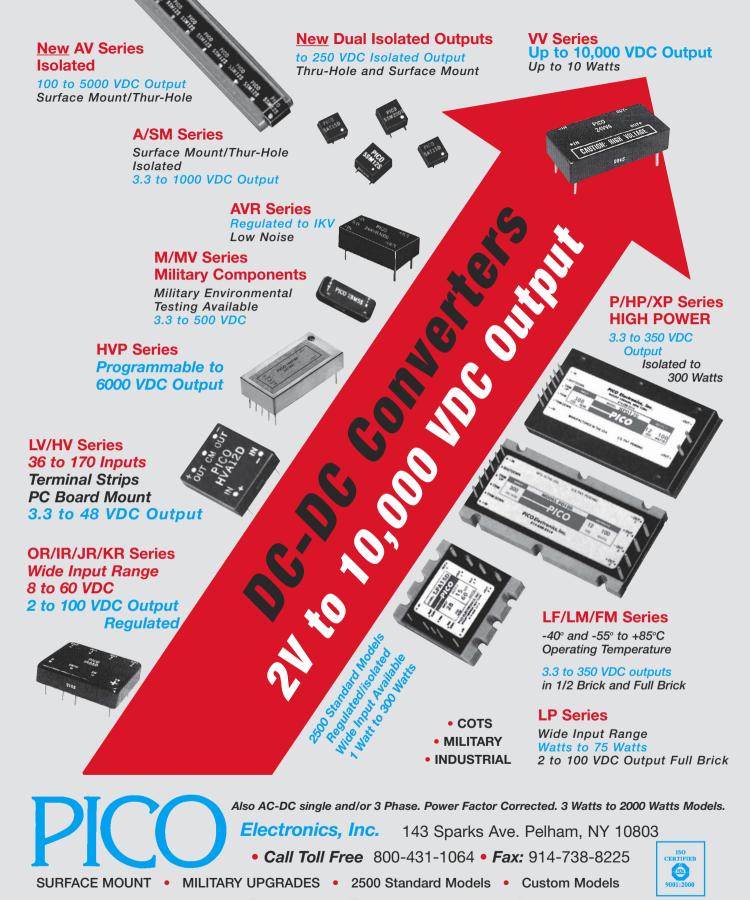

## New High Voltage Hi Power Regulated DC-DC

High Voltage, Isolated Outputs 100-500 VDC

Output Voltages from 5VDC to 500VDC High Power: to 50 Watts, Efficiency to 90%

Miniaturized Size Package: 2.5" X 1.55" X 0.50"

Two Standard Wide Input Ranges

Safe: Short Circuit, Over/Under Voltage, and Over Temperature Protected

Options Available: Expanded Operating Temperature, -55 to +85°C Environmental Screening, Selected from MIL Std. 883

Ruggedized for Operation in Harsh **Environments**

External Bias Control: For Charge **Pump Applications**

Custom Modules: Available to Optimize Your Designs, Special Input or Output Voltages Available

PICO's QP Series compliments our 650 plus existing standard High Voltage Modules. Isolated, Regulated, Programmable, COTS and Custom Modules available to 10,000 Vdc and other High Voltage to 150 Watts!

#### www.picoelectronics.com

E-Mail: info@picoelectronics.com

send direct for free PICO Catalog Call Toll Free 800-431-1064

FAX 914-738-8225 Electronics,Inc.

143 Sparks Ave, Pelham, NY 10803-1837

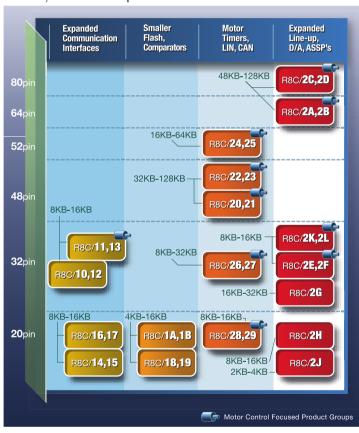

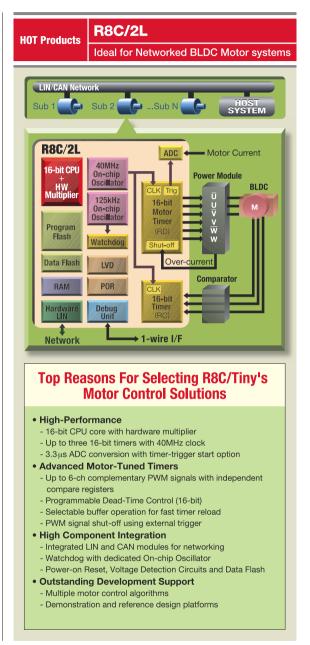

## **R8C/Tiny Improves Efficiency and Adds Intelligence to Motor Systems**

Networked Motors: 40MHz 16-bit Timers and LIN/CAN Modules

## **Renesas Technology**

#### No. 1\* supplier of microcontrollers in the world

introduces R8C/Tiny Series of microcontrollers for low-end motor control applications. Advanced motor-tuned timers coupled with R8C/Tiny's powerful 16-bit CPU provide the performance demanded by applications ranging from electronic toothbrushes to networked motor arrays in industrial automation.

#### **R8C/Tiny Product Lineup**

\*Source: Gartner (March 2007) "2006 Worldwide Microcontroller Vendor Revenue" GJ07168

Get Started Today - Go online and register

to be eligible for a FREE R8C/Tiny Starter Kit \*

www.america.renesas.com/ReachR8C/a

\*Only available to customers in North and South America

Renesas Technology Corp.

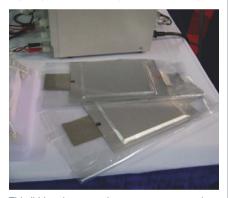

## Lithium-ion capacitor combines more than 100,000 charge cycles, low self-discharge rate

ithium-ion batteries are the current darlings of the automotive world because of their potential for finally making electric vehicles practical. They are not without their drawbacks, however, including their relatively limited cycle life. This problem affects notebook computers, which typically experience batterycapacity decline after a year or so of frequent

This lithium-ion capacitor measures approximately 5×8 in. and has 1100F capacitance.

charge/discharge cycling. Supercapacitors, on the other hand, provide 100,000 cycles with no degradation in capacity. They, too, have an Achilles' heel, however: Leaving them on the shelf for just a day or two can cause them to self-discharge.

JM Energy has now come up with an approach that combines the best features and omits the flaws of both these technologies. The company, an offshoot of petrochemical company JSR Corp (www.jsr.co.jp), has announced a lithium-ion capacitor with energy density of 21to 25 Whr/l, self-discharge of less than 5% after three months, and less than a 10% drop in capacity from initial charge after 100,000 cycles. The units' voltage ranges from 2.2 to 3.8V. The 1000F series has a capacitance of 1100F and an internal dc resistance of 2.5 m $\Omega$ ; the 2000F series has 2200F capacitance and an internal dc resistance of 1.4 m $\Omega$ . JM Energy plans to offer the devices for approximately 10 cents per farad.-by Margery Conner

**⊳JM Energy**, www.jmenergy.co.jp/en.

#### - FEEDBACK LOOP

"The old Army phrase 'screw up and go up' is the normal situation. I've seen and been associated with some great and talented managers, but they're few and far between. Most are incompetent, lazy egomaniacs playing a political game with their upper managers so they get noticed and jump to the next pay scale."

—Reader William Tell, in *EDN*'s Feedback Loop, at www.edn. com/article/CA6578140. Add your comments.

### FPGA IP completes wireless-backhaul method

Wintegra's third-generation UFE3 (universal-front-end-3) IP (intellectual-property) core for high-channel-density, wireless-back-haul designs provides an upgrade path for designers migrating voice-centric cellular systems to high-capacity data-plus-voice-capable designs. The core works with the company's WinPath2 processor and PMC-Sierra's Temux family of framers and mappers. The IP core plus Wintegra's WinPath2 processors at the central office provide bidirectional conversion of 8064 legacy DSO channels to GbE (gigabit Ethernet), with carrier Ethernet as the link to remote cell sites. The core enables a fully channelized application running any protocol from a list that includes PWE3 (pseudowire end-to-end emulation), MC/ML-PPP (multiclass/multilink point-to-point protocol), IMA (inverse multiplexing over

asynchronous transfer mode), and MFR (multilink-frame relay).

A typical example that Wintegra quotes takes an OC (optical-carrier)-12 channel—plus a reserve duplicate channel—from the telecom network and connects it to the PMC-Sierra chip, which interfaces directly to an Altera (www.altera.com) Stratix II FPGA, on which the IP resides. The programmable chip in turn connects to the WinPath2, which bridges the signal to the backplane.

Wintegra supplies the UFE3 soft core for a per-project fee in source code. A reference board from Wintegra features Altera's Stratix II FPGA and PMC-Sierra's Temux 336.

-by Graham Prophet

- **>Wintegra**, www.wintegra.com.

- **PMC-Sierra**, www.pmc-sierra.com.

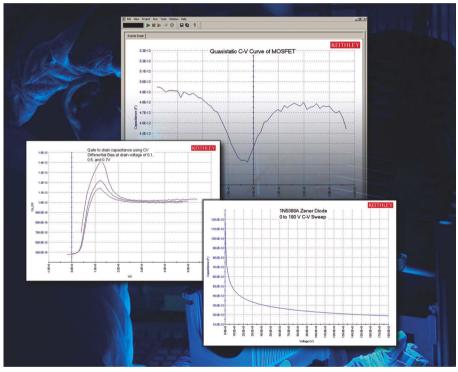

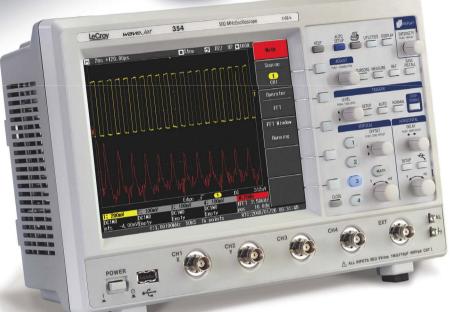

### Keithley debuts software upgrade and switch/multimeter options

eithley Instruments at Semicon West (www. semiconwest.org), which took place in San Francisco last month, introduced Version 7.1 of the KTEI (Keithley Test Environment Interactive) for the company's Model 4200-SCS semiconductor-characterization system. The company also announced an expansion of its Series 3700 system family.

The KTEI software upgrade broadens the capabilities of the Model 4200-CVU (capacitance-voltage unit), offering software support for characterizing high-power semiconductor devices at voltages as high as 200V dc or 400V differential voltage and currents as high as 300 mA. This capability is useful for engineers working with LDMOS (laterally diffused metal-oxide semiconductor) and other high-power semiconductor devices in automotive, display, MEMS (microelectromechanical-system), and other high-power applications. KTEI Version 7.1 also adds software support for

other new functions, including differential-dc bias and quasistatic capacitance/voltage testing. It offers an expanded set of device-test libraries, as well as a variety of software enhancements to speed and simplify testing.

The company added the Model 3724 dual-1X30 solid-state-FET relay-multiplexer card and the Model 3750 multifunction-I/O card to the Series 3700 system switch/ multimeter and plug-in-card family. The Model 3724 card features scanning speeds of greater than 1000 channels/ sec, including measurement, and switch-only scan rates of greater than 1200 channels/ sec. The card also offers 200V, 0.1A switch/carry capacity with offset current of less than 10 nA. You can automatically configure the solid-state relays into either a dual 1×30 or 1×60 multiplexer. The card also features temperaturemeasurement capability with automatic CJC (cold-junctioncompensation) sensors when you use them with the optional screw-terminal accessory.

The Model 3750 multifunction-I/O card features 40 digital-I/O channels with highcurrent-driver outputs that can sink as much as 300 mA, allowing them to directly drive relays without any interface circuitry. The Model 3750 also features two programmable analog outputs offering both voltage- and current-programmable isolated analog outputs, including 0 to 20 mA, 4 to 20 mA, or ±12V dc, It also comes with four totalizers/counters with 32-bit resolution and has a 1-MHz input rate. The Model 3724 sells for \$1595, and the Model 3750 sells for \$1250 (one).-bv Rick Nelson

▶Keithley Instruments, www.keithley.com.

The KTEI software upgrade broadens the capabilities of the Model 4200-CVU, offering software support for characterizing high-power semiconductor devices at voltages as high as 200V dc or 400V differential voltage and currents as high as 300 mA.

#### **DILBERT By Scott Adams**

Low power

Highest functionality in its class

First 65-nm low-cost FPGA

# VERY CCUL

Cool off your system with Altera® Cyclone® III FPGAs. The market's first 65-nm low-cost FPGA features up to 120K logic elements—2X more than the closest competitor—while consuming as little as 170 mW static power. That's an unprecedented combination of low power, high functionality, and low cost—just what you need for your next power-sensitive, high-volume product. Very cool indeed.

www.altera.com

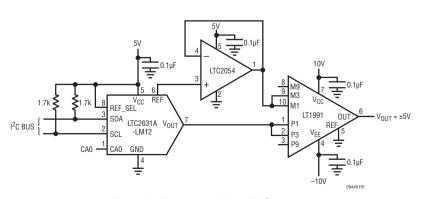

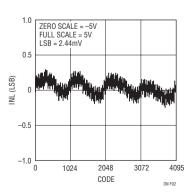

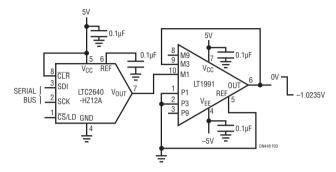

## 16-bit, 10M-sample/sec ADC uses SAR architecture

nalog Devices' new AD7626 ADC provides 16-bit samples at a 10-MHz rate while using 130 mW. The part targets use in digital-X-ray machines, MRI (magnetic-resonance-imaging) systems, and ATE (auto-

matic-test equipment), as well as general data-acquisition, sonar, and other applications. The differential-input device uses digital-LVDS (low-voltage-differential-signaling) outputs and has an internal 4.096V buffered reference,

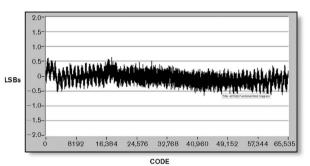

The AD7626 offers an INL of less than 1 bit when it digitizes a 1-kHz input tone at 10M samples/sec.

or you can provide an external reference. A common-mode pin can supply half the reference voltage to the input amplifiers. The device requires both 2.5 and 5V power supplies.

The AD7626 has good dc performance, with a typical INL (integral nonlinearity) of  $\pm 1$  bit, as well as no missing codes over its output range. Typical DNL (differential nonlinearity) is  $\pm 0.3$  bits. The device also offers good ac specs with a 92-dB SNR (signal-to-noise ratio) and an ENOB (effective number of bits) of 15. The part employs a SAR (successive-approximation-register) architecture so that,

unlike a pipelined ADC, each clock cycle immediately produces a valid output. Pipelined converters must clock four to six times for the correct conversion data to work its way through the pipeline and appear at the output. This limitation makes pipelined converters less appropriate in multiplexed-system applications, in which the clock-cycle latency creates more software overhead to ensure that the data is valid for a given channel.

The AD7626 is available in a 5×5-mm, 32-pin LFCSP with a suggested retail price of \$34 (1000). It operates over a −40 to +85°C temperature range. Production quantities and evaluation modules are available now.—by Paul Rako ▶Analog Devices, www. analog.com.

## MULTIARCHITECTURE-DSP ROAD MAP REFINES POWER-EFFICIENCY-VERSUS-PERFORMANCE BALANCE

Texas Instruments' multiarchitecture-processor plans expand a lowpower-design emphasis beyond the fixed-point C550x series of processors and applies it to the high-performance C640x family, the floating-point C674x family, and the highintegration OMAP (Open **Multimedia Applications** Platform)-L1x family of processors. This shift addresses developers' increasing requests for processing options in different power budgets rather than power consumption for a given level of performance. New devices in each of these product lines will support software and pin-for-pin compatibility so that developers can immediately begin design-

devices and then migrate to devices that consume less power.

The first devices available in this lineup are a new generation of the C674x floating-point DSP family; they will become available for sampling in the fourth quarter of 2008, and prices will start at less than \$9 (100). The devices support a deepsleep power draw of 6 mW using a 0.95V core with the real-time clock on and the DSP and all peripheral clocks off. The power draw is 12 mW in standby mode with the same operating scenario but with the PLL (phaselocked loop) enabled. Active power draw is at 420 mW with an operating scenario using a 1.2V core running at 300 MHz;

the McBSP (multichannel buffered serial port), SPI (serial-peripheral interface), and generalpurpose I/Os active; and 50% access of the 16-bit mobile DDR at 133 MHz. These numbers represent one-third the power consumption of the previous floating-point devices with a 20-times improvement in standby power.

TI slates the availability of the other next-genera-

All four of the new processor families emphasize lowpower operation.

tion low-power families for 2009. The C640x devices deliver twice the processing performance of the currently available lowpower DSPs. The C550x devices halve the lowpower operation to 6.8  $\mu$ W in deep-sleep mode, 0.34 mW in standby mode, and 18 mW in active mode using a 1.05V core running at 60 MHz with 75% DMAC (direct-memory-access-controller) usage and 25% addition operations at normal operating temperature. Active power consumption for a 1.3V core running at 100 MHz with 75% DMAC usage and 25% addition operations at normal operating temperature is 46 mW.

−by Robert CravottaTexas Instruments,www.ti.com.

ing with currently available

#### Our newest wireless infrastructure innovations

#### **AD6655 IF Diversity Receiver**

Reduces cost of deployment to allow more base stations to improve network quality. 3G support allows increased capability for high data rate applications.

#### AD9230 Single, 12-Bit 250 MSPS ADC

Better base station power efficiency using digital predistortion techniques reduces electricity demand and provides better spectrum purity.

## AD9788 Dual, 16-Bit 800 MSPS Transmit DAC Simplifies transmit architecture by eliminating

mixing stages and provides best ACLR for enhanced network performance.

#### AD8375 and AD8376 Variable Gain Amplifiers

These VGAs enable excellent dynamic range to capture faint transmitted signals in the presence of strong signals.

#### AD9549 and AD9516 Dual Input Network Clock Generator and Distribution Function

Very low noise clock sources ensure best signal quality across multiple wireless platforms.

## Quality connections—in less space, using less power—that's why more base station engineers speak to Analog Devices

As fast as wireless connectivity became pervasive, Analog Devices data converters became the preferred signal processing standard within base station designs. Today, that data conversion technology is just part of a growing family of analog, digital, RF, and mixed-signal solutions for flexible, software-based radio architectures that support wireless standards from GSM to WiMAX. ADI continues to leverage more than 40 years of signal processing innovation to reduce the size, cost, and power demands of base stations, while enabling increased data rates and delivering the calling experience wireless users prefer. And we offer the same application-tuned advantages for medical, industrial, consumer, and automotive designs.

To experience what Analog Devices can do for wireless infrastructure and for other signal processing designs, call 1-800-AnalogD or visit www.analog.com/basestation.

#### **M RESEARCH UPDATE**

BY MATTHEW MILLER AND ANN STEFFORA MUTSCHLER

## Photonics researchers decelerate light to accelerate data

research team at the USC (University of Southern California) Viterbi School of Engineering has received \$4.3 million in DARPA (Defense Advanced Research Projects Agency) funding to develop continuously tunable optical delays, which could accomplish tasks such as multiplexing entirely in the photonic domain—without the inefficient conversion

of light streams into electronic signals and back again.

The work hinges on passing light of a particular "color," or wavelength, through an element that slows that wavelength. By applying a different color-dependent delay to each of multiple photonic data streams, the researchers enable buffering, interleaving, multiplexing, demultiplexing, and synchroniza-

tion-all without subjecting the speedy streams to the comparative brick wall of an electronic interface. The researchers report that they have successfully delayed an 80-Gbps data stream and multiplexed two 40-Gbps streams. They expect to reach capacity in the hundreds of gigabits per second and aim to produce a system that can delay light by as much as 5 msec, which would represent a 50-fold improvement over the 100-nsec result they have published thus far.

DUSC Viterbi, www.viterbi.

out the inefficient conversion tiplexing, and synchronizausc.edu. INPUT FIBERS WAVELENGTH (COLOR)-DEPENDENT TIME DELAY ΠΑΤΑ PACKET 1 DATA TUNABLE TUNABLE PACKET 2 WAVELENGTH WAVELENGTH CONVERTER CONVERTER DATA PACKET 3

Light-slowing materials permit researchers to introduce wavelength-dependent time delays onto photonic data streams, thus enabling applications such as multiplexing (courtesy USC Viterbi School of Engineering).

#### Kerf-free wafering technology reduces polysilicon for photovoltaics

A 125×125-mm. 50-micron

PolyMax solar wafer has

excellent mechanical and

electrical characteristics.

To substantially reduce the amount of polysilicon within the ingot-to-wafer manufacturing steps and eliminate some of the costly consumables in today's wafer manufacturing, Silicon Genesis has produced solar substrates for photovoltaic applications using

its "kerf-free" wafer-processing technology. The company's PolyMax technology aims to eliminate material losses that occur during sawing; the term kerf refers to the width of the cut a saw blade makes. The company says its technology creates high-efficiency solar cells without sawing, grinding, or

other mechanical thinning of wafers.

The adoption of the technology could help relax the shortage of polysilicon feedstock, according to Silicon Genesis. The company says it has produced 50-micron-thick, 125-mm wafer samples with excellent mechanical

and electrical characteristics. The company plans to start pilot-line operations by spring 2009 to demonstrate kerf-free processing of silicon ingots into wafers ranging from 50 to 150 microns in thickness.

-ASM

Silicon Genesis, www. sigen.net.

#### TECHNOLOGY GIVES WINDOWS A SOLAR EDGE

Researchers at the **Massachusetts Institute** of Technology have developed a technology that transforms a pane of glass into a solar concentrator that can gather light over its entire surface and conduct that light to solar cells along its edges. Employing dyes that trap wavelengths of light inside the pane, the technology can increase the power from solar cells by 40 times, according to the MIT team. Moreover, the technology is simple to manufacture, leading to significant cost savings over current concentrators, which involve mirrors that mechanically track the sun's motion.

A spin-off company, Covalent Solar, hopes to commercialize the technology within three years.—MM

- Massachusetts

Institute of Technology,

www.mit.edu.

- Covalent Solar, www. covalentsolar.com.

A system of organic dyes allows panes of glass to concentrate light for collection by solar cells at the glass' edge (courtesy Donna Coveny, MIT).

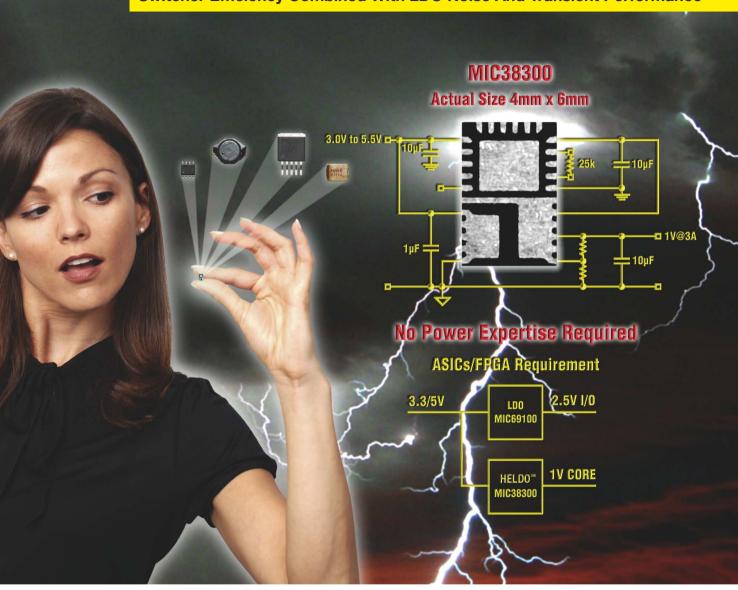

## Power That Gives You The Best Of Both Technology Worlds

**Switcher Efficiency Combined With LDO Noise And Transient Performance**

The MIC38300 is a 3A step down converter and the first device in a new generation of HELDO<sup>TM</sup> products providing the benefits of LDOs with respect to ease of use, fast transient performance, high PSRR and low noise while offering the efficiency of a switching regulator.

As output voltages move lower, the output noise and transient response of a switching regulator become an increasing challenge for designers. By combining a switcher whose output is slaved to the input of a high performance LDO, high efficiency is achieved with a clean low-noise output.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/mic38300.

#### The Good Stuff:

- ◆ 2.2A Continuous operating current

- ◆ Input voltage range: 3.0V to 5.5V

- Adjustable output voltage down to 1.0V

- Output noise less than 5mV

- ◆ Ultra fast transient performance

- ◆ Unique Switcher plus LDO architecture

- Fully integrated MOSFET switches

- Micro-power shutdown

- Easy upgrade from LDO as power dissipation becomes an issue

- Thermal shutdown and current limit protection

- ◆ 4mm × 6mm × 0.9mm MLF ® package

BY LEE HILL

### All about surface-mount ferrites

imple, two-terminal SMT (surface-mount-technology)ferrite-bead components perform crucial functions in many systems. For example, one might suppress electromagnetic emissions from a power wire. Another might provide isolation between a digital circuit and a wireless transceiver. You may be surprised to learn that the performance of a ferrite bead in any power-filtering application can vary by more than a factor of 10, depending on the magnitude of dc current passing

through the part during actual operation. Understanding that behavior under the influence of dc bias can help you create quieter designs and avoid drawing wrong conclusions when troubleshooting.

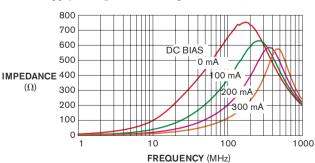

Manufacturers rate all ferrite beads according to a chart that shows impedance magnitude versus frequency (Figure 1). You normally use a ferrite bead in a series-connected noise-blocking configuration. For that application, you should select a ferrite bead with suitably low impedance at dc but high impedance at the frequencies you wish to suppress.

An example involves the 5V-dc supply voltage in a desktop electronic appliance. Assume that the 5V supply provides host power to an external USB port. You may worry that noise from inside the system due to an internal 100-MHz clock might find some low-impedance path backward through the 5V supply circuits, ultimately making its way onto an external power cable. If that situation happens, your system might fail radiated-emissions testing due to radiation from that cable. To attenuate the passage of that noise power, you place a ferrite bead in series with the output of the 5V supply.

What happens to the impedance of that ferrite bead, and hence its noisesuppressing ability, when you plug in an external, host-powered USB de-

> vice? Suppose that, in a quiescent state, the filtered 5V power net draws only 100 mA. Connecting an external USB device causes the device to draw an additional 200 mA through the ferrite bead.

> Figure 1 plots a family of four curves for the ferrite bead. Each curve depicts the relation of impedance to

frequency for some value of dc-bias current. An impedance bridge adds a dc bias to the device under test, generating these curves. According to the plots, changing the current from 100 mA before you plugged in the USB device to 300 mA after you plugged in the device decreases the impedance of the ferrite bead at 100 MHz from 400 to 120 $\Omega$ . Assuming that the emitted radiation varies inversely with the impedance of the ferrite bead, you just increased the radiated emissions by more than 10 dB!

A casual observer might mistakenly conclude that the external USB device caused the increase in emissions. It did, indirectly, but only because the additional dc current draw modified the performance of the ferrite bead. An experienced EMI (electromagnetic-interference) troubleshooter would notice the contravening evidence that the external USB device doesn't even have a 100-MHz oscillator and the noise at 100 MHz was present before he attached the USB device.

In short, remember:

- Don't use a ferrite bead unless you have data showing impedance versus frequency while under the influence of dc-bias current.

- Don't operate ferrite beads close to their maximum rated current; impedance changes markedly as you approach the maximum rated current.

- In general, for any given level of bias current, a larger, 0805-sized ferrite bead exhibits better performance than a smaller, 0603-sized ferrite bead.

Ferrite beads can be tricky, but look on the bright side: You now have a cool little filter whose performance depends on bias current; change the bias and you can tune the filter for optimum noise suppression.EDN

Lee Hill, founding partner of Silent Solutions, teaches classes on electrical-noise reduction, conducts design reviews, and troubleshoots EMI problems. You can reach him at LHill@silent-solutions.com.

+ www.edn.com/signalintegrity

Figure 1 DC-bias current changes the performance of the ferrite bead.

## **Decrease Heat**

## National's PowerWise® solutions provide optimal performance at the lowest power

Find nearly 300 PowerWise products that are top performers in efficiency based on competitive metrics across 24 categories, including:

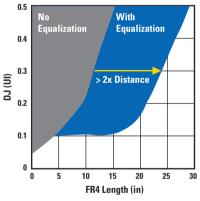

- Power-Saver equalizers more than double signal distance at up to 12.5 Gbps while consuming zero power

- Synchronous switching regulators are ≥95% efficiency for point-of-load conversion applications

- High-voltage PWM controllers convert input voltages up to 100V at ≥85% peak efficiency

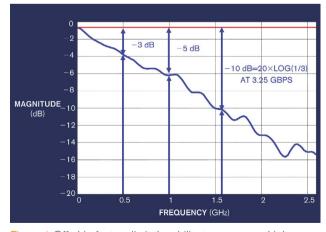

DS80EP100 12.5 Gbps Power-Saver Equalizer performance graph

High-precision temperature sensors feature TruTherm® technology for >0.75°C accuracy with greater thermal and fan speed control

Find PowerWise products, metrics, white papers, app notes and tools at:

national.com/powerwise

lational Semiconductor Corporation. National Semiconductor, 🔗 and PowerWise are registered trademarks. All right

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

## IP selection and power supplies

ith the "greening" of electronics and IC systems, power-supply strategies are critical portions of the IP (intellectual-property)-selection process. There are two major competing power-analysis standards in the EDA world: the Accellera (www.accellera.org)-coordinated UPF (Unified Power Format) and the Codence (www.scdence.com)/Si2 (www.si2.org)-coordinated CPF (Competition of the Codence.com)

Cadence (www.cadence.com)/Si2 (www.si2.org)-coordinated CPF (Common Power Format). Application organizations, such as the Consumer

Electronics Association, also drive power-measurement and -analysis standards. In response to the multiple formats, IP providers have not fully adopted any one side to avoid the risk of limiting their potential client bases. This failure to fully embrace just one of the standards, however, has caused confusion and uncertainty in IP users about power-strategy compatibility.

This uncertainty is a problem for several reasons. First, design groups need power-supply standards because they are trying to enhance the RTL (register-transfer-level) netlists by including power supplies in their connectivity. As a result, the design groups need to understand the source and management of the power.

More important, as the designs are going green, multimode power is key. Once again, there is variety: IP developers use several power-management techniques in different applications and for different circuits. For dynamic-power management, designers might employ simple logic optimization, clock gating, multithreshold voltage, or DVFS (dynamic-voltage and frequency scaling). Power gating, multithreshold design, and multithreshold CMOS are methods designers might employ for leakage-power

A recently emerged option for mobile and small-form-factor applications is the use of through-silicon vias.

management. It is difficult and consumes a great deal of conversion logic to have a large function comprising multiple IP blocks using multiple power-management techniques.

Because there are multiple power solutions, and because these approaches have backing from different EDA vendors, you have to make sure that your IP is compatible with the EDA tools you are using. Both the UPFand the CPF-specification formats have recommended methods, tools, and techniques for dealing with logic, clocks, and memories, as well as with other hard-IP blocks. However, the formats do not contain the same information and do not guarantee conformance or interoperability of blocks from different IP suppliers at different stages of the design process on different tools. You can obtain information from www.accellera.org/activities/upf and www.si2.org/?page=811.

From a functional point of view, the most important aspect of the power management for a design is the long-standing issue of process-isolation techniques for the applications of power. Power-reduction requirements not-withstanding, it is still important that fast-switching, high-noise power is not near or connected to high-sensitivity circuits. For that reason, designs still need multiple functional power rails for core power, memory power, I/O power, analog power, display power, and the like.

One of the last issues for IP selection—and one that designers often miss—is the type of package that will house the end product. Traditional designs employ edge-oriented I/Os, which use standard interconnect techniques to get from the circuit to the power pads. A large number of highpin-count designs use core I/O, which is a generic term for pads that are in the middle of the chip directly over active circuitry. Designs that use core I/O can have just power supplies, just signals, or both power supplies and signals on these pads. The IP blocks must accommodate the effects of the mechanical stress that both the pads and the pads' electrical-performance issues cause. A recently emerged option that is increasingly popular for mobile and small-form-factor applications is the use of TSVs (through-silicon vias) in and around IP blocks, TSVs for stacked and 3-D die interconnect have significant die-to-die modeling and verification issues. You must develop third-party IP for applications that will employ TSVs in close cooperation with the IP provider and system-design group.EDN

Contact me at pallabc@siliconmap.net.

- + Go to www.edn.com/080821pc and click on Feedback Loop to post a comment on this column.

- + More at www.edn.com/tapeout

## In your complex world...

...only Keithley delivers an intuitive, integrated, one-box solution for DC I-V, pulse, and C-V characterization

- Integrate multiple test types easily into a single automated test sequence.

- Save time with our extensive C-V test library and built-in parameter extractions.

- Get your system up and running quickly and simply with turnkey application packages.

- Don't get stuck with obsolete hardware get a system engineered to grow with you costeffectively as your test requirements evolve.

Go to www.keithley.com/one and try a demo.

## TAPE-OUT COMES A LOT FASTER WITH CALIBRE nmDRC.

INTEGRATED SYSTEM DESIGN + DESIGN FOR MANUFACTURING + ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

Calibre® nmDRC | There's nothing like having an advantage when you're racing to market. That's exactly what you get with Calibre nmDRC. Widely recognized as the world's most popular physical verification solution, Calibre's hyperscaling architecture produces the fastest run times available. To accelerate things even more, Calibre nmDRC adds incremental verification and a dynamic results-viewing and debugging environment. Designers can check, fix and re-verify DRC violations in parallel, dramatically reducing total cycle time. Start out and stay ahead of the pack. Go to mentor.com/go/calibre\_nmdrc or call us at 800.547.3000.

### SPECIFYING, TESTING, AND MONITORING A BATTERY PACK

typical laptop-computer battery pack can contain more than 50 Whr of energy and requires care in its design, construction, and operation to ensure that it remains safely within its operating limits. Few circuit-design engineers want or need to become battery experts, yet they must ensure that a system's battery pack can safely perform its tasks and that the host system can monitor the pack during operation. To address these constraints, you must understand how to specify a battery pack, what type of test and inspection it requires, and how the application monitors the battery pack's health during operation.

High energy capacity has made lithium ion the dominant battery chemistry for portable consumer devices (Reference 1). However, safety concerns also force the need for manufacturers to package the cells in a battery pack that often includes fuses, monitoring circuitry, a fuel gauge, an SMBus (system-management-bus) interface, and authentication circuitry. The industry-standard 18650 cell is about the same size as a AA bat-

tery, but even single-cell devices require that cell to be in a battery pack, complete with safety circuits and fusing.

Chemistry and technology features aside, you must select a lithium-ion-cell vendor with a stable supply chain to ensure a reliable source of packs and cells. For a variety of reasons, including recent years' massive recalls, factory shutdowns, and materials shortages, it's increasingly difficult to obtain lithium-ion cells.

Couple those problems with increasing transportation costs; a poor exchange rate; increased demand for lithium-ion batteries in consumer electronics, power tools, and cars; and the rising price of cells, and you'll see why you must make a reliable supply chain a priority in selecting a cell supplier.

In the early 1990s, Sony became the first to manufacture lithium-ion cells, and the company, along with Panasonic, remains one of the largest cell vendors. Cost-sensitive, low- to medium-volume products can get by with off-the-shelf battery packs, which are available from thousands of small and midsized Chinese vendors. Don't be a penny-pincher when selecting a battery pack, however: It's seldom cost-effective to attempt to test-in quality at incoming inspection, and battery-pack field failures are dangerous liabilities. For cost-conscious, low-volume applications, an off-theshelf pack is a valid route, but don't rely on price as the determining factor. Highvolume applications can often justify

## "I need an affordable power supply that won't risk my DUTs."

### Done. And we added memory, too.

Introducing the Agilent U8000 Series single-output, non-programmable power supply. It comes packed with more features than you'd normally expect in an affordable power supply. Fully integrated overvoltage and overcurrent protection keep your DUTs safe while you work. A keypad lock and physical lock provide added security. And, the capability to save and recall up to three memory states shortens set-up time and reduces mistakes.

What's more, it's an evolution of the best-selling Agilent E3600 Series and

- Power Range 90 W to 150 W

- Voltage/Current Range up to 30 V/5 A

backed by 40 years of experience in power supplies, so you know it has reliability you can count on.

For more on the U8000 Series, www.agilent.com/find/agilentu8000

the costs of developing a custom battery pack. In addition, low- to midsized-volume applications requiring high quality and high power, such as medical applications, can command a higher price and also can warrant a custom pack.

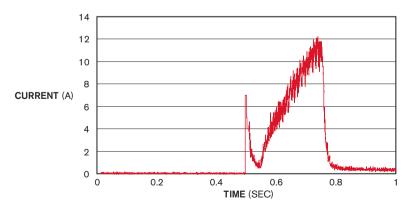

You can work with the battery-cell vendor or a battery-pack-design house to develop a custom battery pack. A valuable communication tool when working with your battery-pack vendor is a set of power curves that shows your application's profile over time during different operating modes, including temperature extremes. A power tool might have a discharge curve with high current spikes corresponding to cutting or drilling tasks (Figure 1). The magnitude and the duration of the spike vary with the shape of the material. A device that includes a radio transceiver also has spikes during transmission, and a continuous current must power its display and other functions. Ask your battery-pack vendor to demonstrate with prototype packs that its design can meet the demands you specify in all of your power curves.

Some medical-application customers of custom-battery-pack-design and-manufacturing vendor Micro Power Electronics require the company to test every battery and include a full charge-and-discharge cycle to ensure that the company has properly assembled each pack and provided it with sufficient capacity, according to Robin Tichy, marketing manager at Micro Power. In some cases, the company must develop a custom tester for the manufacturing line.

#### AT A GLANCE

- ► Higher-quality cells and more sophisticated battery-management circuitry can pay off in lower battery-pack-production costs.

- Battery characteristics that enhance life cycles and charge times can be differentiating features for your battery pack.

- Higher-priced as well as highervolume products can justify the higher upfront costs of customized cells and battery packs.

Some customers require just a simple voltage test to ensure proper assembly; others require that the manufacturers perform the tests on only a sampling of products.

If your battery-pack design calls for a relatively inexpensive fuel-gauge IC that counts coulombs by calibrating the pack and by measuring the charge to and from the battery, then you must individually charge and discharge each battery pack after assembly. This calibration increases production cost and the overall battery-pack price. Tichy suggests that you weigh the trade-offs of a more expensive fuel gauge, such as Texas Instruments' Impedance Track family, which requires no initial charge-and-discharge cycle.

IEEE standard 1625 for rechargeable batteries for portable computing covers testing requirements for laptopcomputer-battery packs (**Reference 2**). After Dell, Hewlett-Packard, Apple, and other laptop-computer manufac-

Figure 1 The system designer documents how the application uses power through power, or "discharge," curves. In this example of a battery pack for a screwdriver with a set screw, high current spikes correspond with cutting or drilling events. These events change depending on the duration of the spike and the material the drill is cutting.

- **Switching Regulators**

- Non-Isolated PWM Controllers

- Isolated PWM Controllers

- **Power MOSFET Drivers**

- Hot Plug Controllers

- ORing FET Controllers

- Supervisors

- Power Sequencers

- Linear/LDO Regulators

intersil.com/power

the EVOLUTION of ANALOG™

## **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

### The Difference Between Different Differential Amplifiers

**Q.** I'm perplexed. Why is the output voltage of my ADC differential amplifier driver not what it should be?

A. It's probably related to the type of differential amplifier you've selected. Often, when we exam a customers schematic, we find the amplifier is behaving exactly as it was designed to. The problem turns out to be something as simple as not being familiar with the differential amplifier.

Selecting the right differential amplifier is sort of like picking a new car. There are many models to choose from, and each are packed with various options and features. They all do essentially the same thing: get you from point A to point B. However they all have their own subtleties and that is where the trouble can begin.

When selecting a differential amplifier, the options and features really matter. The three essential classes of differential amplifiers are the sports car, the mid-size and the economy; each class has a little something different to offer.<sup>1</sup>

The sports car differential amplifiers run at the highest frequencies. This class of differential amplifiers features gigahertz bandwidths, ten thousand volts-per-microsecond slew rates, a VCM pin that adjusts input and output common mode voltage, ultralow distortion, and single-ended or differential input drive capabilities. These amplifiers typically find use in broadband and IF communication applications.

The mid-size operates in the hundreds of megahertz range, has low distortion, excellent DC performance, output gain balance and phase matching, suppressing even order harmonics, high slew rate, single-ended or differential input drive capability, a VOCM pin that easily adjusts the output common mode voltage. Some models are

even available as duals. This device is used in communications and instrumentation systems to name a few applications.

The economy model comprises a pair of amplifiers integrated with gain-setting and feedback resistors in a single package, simplifying the design and saving board space. This model provides high input impedance, low power and low noise. The device is typically used with a single-ended input and has unbalanced differential outputs. It operates in the tens of megahertz range, and is usually found in low-power precision applications.

So, next time you're in the market for a differential amplifier, take a walk around the lot, kick the tires and take one out for a test ride (simulation). You'll be glad you did. As always, don't forget to read the owners manual (datasheet) front to back; it can save you a lot of time and help ensure you get the most out of your differential amplifier.

<sup>1</sup> To match up ADI part numbers and the various car models check out the link below.

To Learn More About

Differential Amplifiers

Go to: http://rbi.ims.ca/5719-101

Contributing Writer

John Ardizzoni is an

Application Engineer

at Analog Devices in

the High Speed Amplifier Group. John

joined Analog Devices

in 2002, he received his

BSEE from Merrimack

College in 1988 and

has over 28 years

experience in the

electronics industry.

Have a question involving a perplexing or unusual analog problem? Submit your question to:

rag@reedbusiness.com

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

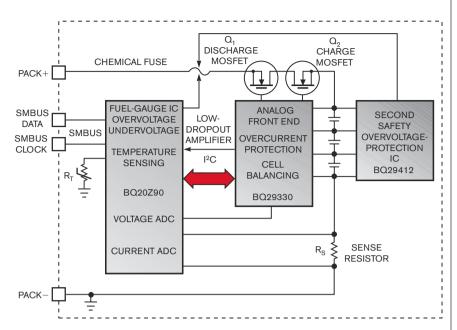

Figure 2 Smart-battery-pack electronics include a fuel gauge, an analog front end, and an overvoltage-protection IC. If the pack exceeds any of several safety conditions, such as overvoltage, overcurrent, or overtemperature, the pack can temporarily disconnect the lithium-ion cells through the safety MOSFETs or permanently disable the battery pack by blowing the chemical fuse.

turers recalled battery packs, the IEEE announced in late 2006 that it was revising the test requirements that IEEE 1625 specifies. The organization is still revising the standard and plans to release it in 2009 (Reference 3). Another standard, IEEE 1725, targets cell-phone and battery-pack testing. In addition, UL (Underwriter Laboratories) 1642 covers electrical, mechanical, and environmental tests for lithium-ion batteries. Rick Chamberlain, vice president of engineering at battery vendor Boston-Power, says that the industry views the UL 1642 specification as the minimum test, especially in the laptop-computer market, and most manufacturers in that segment do more testing to ensure battery-pack safety.

Battery-pack characteristics can also serve as differentiating features that your customers may be willing to pay more for or that may simply influence their purchasing decision. For example, customers may be willing to pay more for a product with a battery pack that offers a longer runtime between charges or a shorter charge time. Similarly, the total cost of ownership of a battery pack for the end user encompasses more than just the cell, power-management circuit,

and packaging; it also includes the number of life cycles: More cycles mean a longer battery life.

Lithium-ion cells are not commodity items, but you can fine-tune them by varying their anode and cathode chemistry, their thickness, and their internalseparator composition. Chamberlain suggests that system designers interview cell suppliers and battery-pack designers to select the cell or even to customdesign a cell to target the performance needs and form factor of their designs. Boston-Power's initial product offering, which it announced in 2007, was the Sonata battery pack, which designers could use in available notebook-computer designs. Sonata's debut coincided with Dell's and Sony's battery recalls. Sonata's safety features included morestable chemical reactions within the cells, proprietary current-control circuits, new thermal fuses, and pressurerelief vents.

Chamberlain points to the cell configuration within the Sonata as an example of how safety concerns complement performance needs in battery-pack design. "A typical notebook battery pack will have an arrangement of six cells in a three-series, two-parallel configura-

the EVOLUTION of ANALOG™

ntersi

## Precisely What You Need!

- Micropower Precision Op Amps

- Instrumentation

Amplifiers

- Current-Sensing Amplifiers

- Precision Voltage References

- Analog-to-Digital Converters

- Digital Potentiometers (DCPs)

intersil.com/pinpoint

the EVOLUTION of ANALOG™

tion," he says. "The current splits as it goes through the paralleled cells, and, because there are slight differences in the impedance characteristics of those cells, the current goes through those cells in slightly different ways and can lead to differences in cell aging and safety concerns. The Sonata cell has a larger [than normal] format: We put three cells in series and have no parallel cells. That [arrangement] sounds relatively simple, but that type of change can offer a lot of performance and safety improvements in a battery pack."

Another example of cell customization is electrode thickness: By controlling the thickness, you can optimize for either high energy storage or high power. The leadtime for including a customized cell needn't be long: You can tweak one of the chemicals in the cell with as little as six months leadtime, according to Chamberlain. Other more significant changes could take more time. "Unless you have that discussion [with a cell supplier]," however, he says, "you'll never know."

Because a battery pack comprises electronics as well as lithium-ion cells, it's important that the system designer and battery-pack designer collaborate and understand the role the pack's power-management electronics play in ensuring both safety and performance. Smart battery packs, which can communicate with the host to report the battery's state of charge and batteryhealth conditions, such as life cycle, temperature, charge and discharge current, and voltage thresholds, offer the highest level of safety and performance. This electronic circuitry is usually part of the battery-pack fuel gauge, the same circuit responsible for the battery-life symbol on a laptop computer's or a cell phone's display.

A battery-pack electronic circuit can have a fuel-gauge IC; an analog front end, including overcharge protection and cell balancing; and an overvoltage-protection IC (Figure 2). If a battery pack's temperature exceeds a preset limit, usually 50°C, then the fuel-gauge-safety circuit will temporarily shut down the pack through one of the two charge-and-discharge safety MOSFETs that are in series with the pack cells. Once the temperature drops to within the operating-temperature

- + For more on accurate lithium-ion-battery fuel gauges, go to www.edn.com/blog/1470000147/post/550029855.

- + For more on requirements for large-format lithium-ion-battery tests, visit www.edn.com/blog/1470000147/post/430029643.html.

- Go to www.edn.com/080821df for more information on the vendors this article mentions. You can also click on Feedback Loop to post a comment on this article.

- + For more technical articles, go to www.edn.com/ednfeatures.

range, the circuit turns the MOSFET back on, and the battery pack recovers.

You may have experienced this situation when your cell phone or laptop computer shuts down after exposure to the sun or after sitting too long in a hot car. The unit then comes back to life after a cool-down period. However, if its temperature remains high or the current remains in an unsafe range, then the circuitry can permanently disable the battery pack by blowing a chemical fuse. Once the chemical fuse blows, the pack is unsalvageable, and its next stop is the recycling center.**EDN**

#### REFERENCES

- Conner, Margery, "Portable power: Features abound, thanks to new battery chemistries," *EDN*, Nov 22, 2007, pg 46, www.edn.com/article/CA6501082.

- 1625-2004, IEEE standard for rechargeable batteries for portable computing, IEEE, 2004, E-ISBN: 0-7381-4012-0, ISBN: 0-7381-4012-0, http://ieeexplore.ieee.org/xpl/freeabs\_all.jsp?tp=&arnumber=1309986&isnumber=29080.

- "IEEE begins revision of laptop battery standard," http://standards.ieee. org/announcements/pr\_P1625\_ guidelines.html.

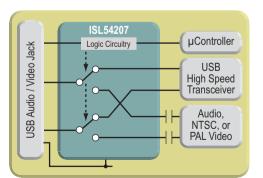

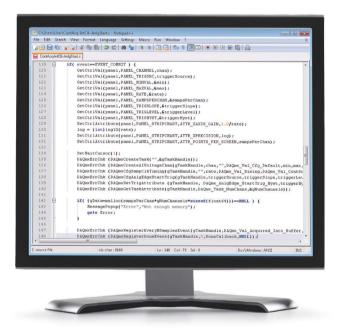

Intersil's tiny USB Switch enables charging, audio, video, and high speed data through a single connector.

Combined data, audio, and video switch eliminates either the USB or TV OUT connector on cameras or media players.

#### Audio / Video / Data

| Device   | Audio THD<br>32Ω (%) | USB<br>Speed | Video Diff<br>Gain Phase |

|----------|----------------------|--------------|--------------------------|

| ISL54207 | 0.06                 | 480          | 0.28 / 0.04              |

| ISL54208 | 0.06                 | 480          | 0.28 / 0.04              |

| ISL54415 | 0.007                | 12           | 0.04 / 0.03              |

| ISL54416 | 0.007                | 12           | 0.04 / 0.03              |

| ISL54417 | 0.007                | 12           | 0.04 / 0.03              |

#### Audio / Data

| Device    | Audio THD<br>32Ω (%) | USB<br>Speed |

|-----------|----------------------|--------------|

| ISL54205A | 0.06                 | 480          |

| ISL54206  | 0.06                 | 480          |

| ISL54400  | 0.007                | 12           |

| ISL54401  | 0.007                | 12           |

| ISL54402  | 0.007                | 12           |

Go to **www.intersil.com** for samples, datasheets and support

Intersil – Amplify your performance with advanced signal processing.

ntersil®

### **ELECTRONIC-SYSTEM-LEVEL DESIGN:**

# IS THERE FIRE BENEATH THE SIM KE?

t was a shimmering promise on the horizon: As SOCs (systems on chips) became more complex, we would simply move from RTL (register-transfer level) to the next-higher level of abstraction—what some experts called ESL (electronicsystem-level) design. We would express the behavior of the system in a high-level language, such as C++. We would model and explore the system at that level, partition it into hardware and software components, and then push a button. Scripts and ESL-synthesis tools would digest our ESL design and give us back a nearly optimal RTL design or even a netlist together with the necessary software. Design productivity would once again be ahead of complexity.

But that was, as they say, then. Today, many failures, false claims, and too-limited tools later, many designers put ESL in the same category as gallium arsenide: a permanent technology of the future. Yet, this dismissal is as inaccurate as some of those early claims of mission accomplished. ESL tools today play key roles in many teams' design flows. Those roles differ in different teams and application areas. But the results are sufficiently important that a design manager today dismisses ESL at his own peril.

### **CONFUSION AND VARIETY**

"In reality, most of what we call power users have been using ESL tools since about 2004," says Gary Smith, noted industry analyst and founder of Gary Smith EDA. "But many of those tools have been internally created, and there has been a lot of confusion about just what is an ESL tool."

The confusion is understandable. There are several levels of abstraction hiding under the title "system-level." And there are many kinds of tools, with different expectations, at each of those levels.

"The initial idea was that ESL was about architectural design," Smith says. This process is far simpler than pushbutton behavioral synthesis. It simply means a textual, executable representation of a system architecture that would allow experimentation at a very high level—sort of a language-based version of the timehonored architectural-design tools, the white board and the spreadsheet.

"But, in 2004, the tools were consumer-application-focused and really were for algorithm design, not architectural design," Smith continues. "There wasn't any focus on the level of abstraction that included blocks like processors and memories."

Even within the algorithm area, there were—and remain—strong differences. Some designers see an algebra-based tool such as the MathWorks' Matlab as the natural way to describe and manipulate algorithms. Others believe C or C++ should play that role, even though these languages carry a strong syntactic bias toward a particular legacy implementation—the Digital Equipment PDP-11 minicomputer. Still others believe that algorithm development should occur in a purpose-built language for describing algorithms—neither purely algebraic nor purely procedural and sequential. This last point of view nearly died out when a generation of interesting languages languished in disuse a few years ago, but it is now making a revival. "The appearance of multicore processing in the SOC world has spurred lots of new work on ESL tools," Smith observes.

A different view of ESL comes from project leaders who are simply trying to get an earlier start on software develop-

ment. In these projects, designers use ESL tools to create a software-based virtual prototype. Designers merge the prototype with, for example, driver code they are developing and test the integrated software system much as they will later test the code running on the real hardware.

Others still feel that the proper emphasis of ESL should be on the architectural level of implementation, not on simply expressing the algorithm. This notion has led to languages—primarily C-derived—and tools that attempt to describe an implementation at an abstract level and either attach to it or infer from it as much information as possible about the structure, timing, and—increasingly—energy consumption of the RTL design it implies. There has been recent work here, as well.

With all of these approaches, expectations, and needs, there is certain to be confusion. Perhaps the best way to clarify the situation is to talk with some design teams who are actually using the tools at these various levels (see sidebar "Look into the future").

#### **ALGORITHM DEVELOPMENT**

Especially in the world of digital-signal processing, just getting the algorithm correct can be a major part of the design process. This challenge has at least two phases: getting the mathemat-

#### AT A GLANCE

- ▶ Pushbutton synthesis of ESL (electronic-system-level) design to a full-chip netlist remains a dream.

- Engineers are using ESL tools in limited ways in some applications.

- System exploration and modeling can work well.

- Synthesis of algorithmic C to RTL (register-transfer level) works for datapaths.

- ➤ Tool developers are gradually expanding the ability to synthesize more-general RTL from C.

ics right and getting the translation from mathematics to hardware and software right. As Smith observes, this problem allowed perhaps the earliest successful uses of ESL tools, and it continues to be important.

Bob Davenport, DSP and system-design consultant with MC2 Technology Group, uses ESL tools in this way. He is a fan of Agilent's SystemVue, a block-diagram-driven exploration environment that finds use in signal processing in communications and media-processing applications. Davenport says that he uses the tool for developing algorithms—often assembling them from functional libraries that are part of the environment—exploring them, and then generating C code, which he then

passes to Texas Instruments Code Composer Studio for optimization.

"For example, we may start with equations for a phase-locked loop, model it, and analyze its performance," Davenport says. "Then, we can generate data, graph it, and use the graphs in reports."